Параллельно компанией велась работа по созданию перспективного семейства компьютеров на базе нового микропроцессора, которое должно было прийти на смену серверам и рабочим станциям UltraSPARC.

Разработка нового семейства включала в себя внесение в архитектуру изменений, вызванных отличиями в интерфейсах процессоров UltraSPARC III и UltraSPARC II, и создание нового набора вспомогательных кристаллов.

Изготовление процессора UltraSPARC III планировалось организовать на фирме Texas Instruments, а первый кристалл ожидался в середине 1998 года. Однако, в силу причин, которые не были обнародованы, сроки появления несколько раз откладывались. В результате, первый опытный образец появился лишь в конце мая этого года, то есть почти на год позже анонсированной даты.

Не стоит воспринимать эту задержку как большую трагедию, поскольку помимо очевидных минусов она имеет ряд положительных аспектов.

Во-первых, для разработчиков дополнительное время никогда не бывает лишним. Если задержки были связаны с какими-либо техническими или технологическими проблемами, то их решение можно рассматривать только с положительной стороны, поскольку рано или поздно они все равно проявились бы.

Во-вторых, дополнительное время получили разработчики собственно систем на базе нового процессора. Вполне вероятно, что рабочие станции и серверы, чье появление планировалось на начало этого года, претерпели какие-либо изменения, может быть даже в части архитектуры.

И, наконец, в-третьих, была обнародована стратегия компании на ближайшие несколько лет. Конечно, это утверждение выглядит спорным, однако, то, что планы по разработке микропроцессоров были представлены именно в тот момент, когда задержки появления очередного процессора стали вызывать определенное беспокойство пользователей, представляется отнюдь не случайным. Это заявление можно рассматривать как очень серьезный и ответственный шаг компании по укреплению собственной позиции на рынке. С одной стороны, это успокаивает пользователей (рассеивает возникшие сомнения), а с другой – бросает вызов другим производителям микропроцессоров, среди которых предоставить долгосрочную программу развития микропроцессоров могут такие компании, как Intel, Compaq, Hewlett-Packard, SGI/MIPS и IBM.

Что же касается собственно задержки, то аналогичные ситуации происходили и у других производителей, включая вышеназванных. Так, например, при проектировании Alpha 21264 потребовалось несколько дополнительных месяцев на моделирование его работы, а появление Intel'овского процессора Merced отложено до середины 2000 года.

2. Политика Sun и основные направления в области разработки микропроцессоров

2.1. Формирование политики

Sun является одной из немногих компаний, разрабатывающих вычислительные системы от начала до конца, то есть от микропроцессоров и архитектуры вычислительной системы до программного обеспечения, поэтому все этапы разработки проходят в рамках единой концепции, что дает определенные преимущества по сравнению с конкурентами (компания имеет больше степеней свободы), но, вместе с тем, накладывает большую ответственность за принимаемые решения.

Основной девиз компании – «Сеть – это компьютер», очень хорошо согласуется с основными тенденциями развития вычислительной техники в последние годы. Так, все большее распространение получают такие области применения, как Интернет и сетевые вычисления. Это, в свою очередь, предъявляет повышенные требования к производительности вычислительных систем, причем потребности в увеличении производительности растут быстрее, чем производительность отдельных микропроцессоров.

Решить данную проблему можно только посредством создания масштабируемых многопроцессорных систем. Так, по словам Криса Вилларда (Chris Willard), руководителя направления исследований в области высокопроизводительных вычислений компании IDC Research, все новшества в компьютерных архитектурах направлены на объединение большого числа процессоров в единую систему. Sun не является исключением в данном вопросе, однако, решение его начинается еще на уровне микропроцессора, а не системы, как у многих других (см. [3]).

Здесь уместно привести слова Ананта Агравала (Anant Agrawal), вице-президента и генерального менеджера подразделения микроэлектроники Sun Microsystems: «На экспоненциальный рост Интернет и сетевых вычислений рынок отвечает требованием высокопроизводительных процессоров, которые должны быть хорошо масштабируемыми. Ultra SPARC III будет удовлетворять этим требованиям и позволит нашим потребителям создавать высокопроизводительные, многопроцессорные системы, которые можно будет легко нарастить, чтобы обеспечить поддержку быстро разрастающейся инфраструктуры» (см. [3]).

Ниже мы рассмотрим конкретные архитектурные решения, заложенные в новый процессор, но перед этим хотелось бы остановиться на стратегии и планах компании в области производства микропроцессоров.

В течение нескольких последних лет компания Sun Microsystems помимо основного направления – процессоров для серверов и рабочих станций поддерживает линию процессоров для встроенных применений (microSPARC). В 1997 году модельный ряд компании обогатился микропроцессором UltraSPARC IIi, предназначенным для использования в недорогих однопроцессорных системах. При этом снижение стоимости системы достигалось за счет использования шины PCI в качестве системной (как в процессоре, так и в самой системе), что позволяло применять периферийные платы данного стандарта от других производителей, а также уменьшить число специализированных СБИС.

В 1998 году компанией была обнародована новая политика в отношении производства микропроцессоров. Необходимость такого шага (как уже упоминалось ранее) отчасти была обусловлена задержками в появлении нового микропроцессора UltraSPARC III и связанной с этим необходимостью успокоить потребителей. С другой стороны, на это повлиял приобретенный опыт производства нескольких типов микропроцессоров, а также анализ рынка. Возможно, был учтен опыт других компаний, занимающихся разработкой и производством процессоров.

В последние годы в маркетинговой политике Sun четко прослеживается тенденция к освоению новых секторов рынка вычислительных систем. Так, например, в середине 90-х компания обозначила свое присутствие в области многопроцессорных комплексов (сначала это были SPARCcenter 2000 и SPARCserver 1000, а затем – Ultra Enterprise 10000). Позже Sun проявила интерес к недорогим системам с шиной PCI.

Такая политика представляется более гибкой и позволяет быстрее реагировать на потребности рынка, а также снижает риски компании по сравнению с ситуацией, когда делается ставка только на одно направление. Возвращаясь к ситуации 1998 года, можно сказать, что в тот момент выбранная стратегия подтвердила свою жизнеспособность.

2.2. Стратегия компании на ближайшие несколько лет

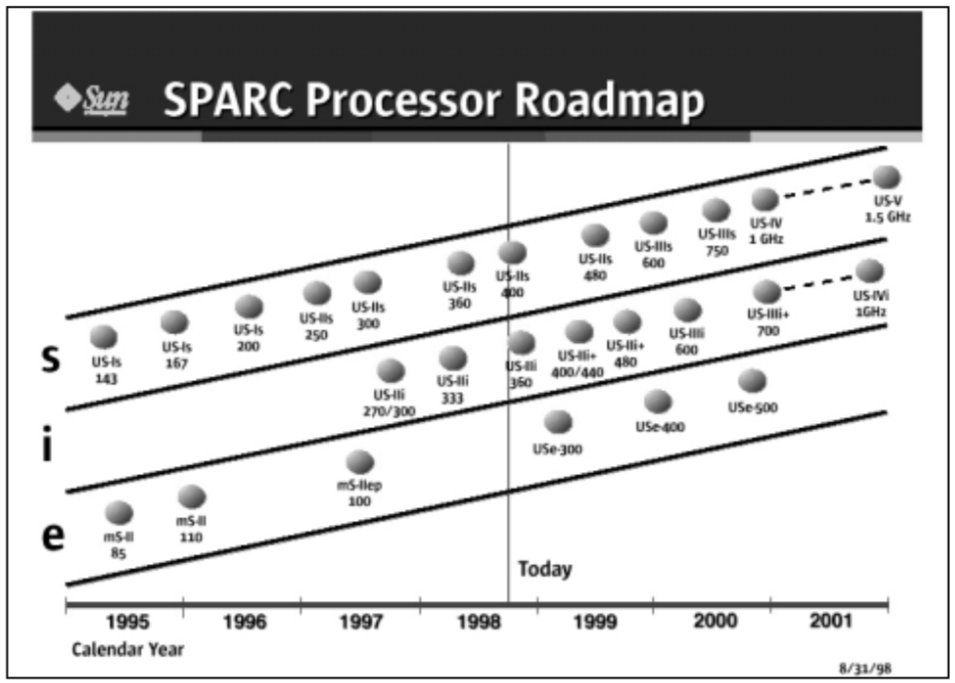

В настоящее время разработка и производство микропроцессоров осуществляется по трем основным направлениям (см. рис. 1, заимствованный нами из [2]). Процессоры, принадлежащие к тому или иному семейству, имеют соответствующий буквенный индекс.

Семейство «S». Сюда входят микропроцессоры UltraSPARC I/II/III. Представители этого семейства обладают полным набором функций и имеют максимальную производительность. Они предназначены для использования в рабочих станциях и серверах с наращиваемой архитектурой.

Семейство «I». Сейчас к нему относятся только микропроцессоры UltraSPARC IIi. Процессоры данного семейства предназначены для использования в однопроцессорных системах, имеющих высокое соотношение производительность/стоимость. Это достигается за счет оптимизации внешних интерфейсов процессора, размещения части функциональных устройств (например, контроллеров интерфейсов) непосредственно на кристалле процессора и сокращения за счет этого числа внешних специализированных микросхем. В будущем предполагается появление конфигураций с несколькими процессорами.

Семейство «E». На сегодняшний день семейство представлено микропроцессорами двух типов: microSPARC и UltraSPARC. Предназначено для встроенных применений (сетевые интерфейсы, платы управления, модемы и т.п.), требующих достаточной вычислительной мощности при минимальной стоимости и низком энерговыделении.

Разработка любого микропроцессора включает в себя три основные фазы: разработку набора команд, разработку собственно архитектуры и выбор технологического процесса. Каждая фаза требует решения целого комплекса вопросов. И с этой точки зрения подход Sun к процессу разработки являет собой пример осторожности. В основу положен принцип минимального риска. При модернизации или разработке нового процессора кардинальному изменению может быть подвергнута только одна из трех составляющих.

Если говорить о конкретных процессорах UltraSPARC, то компания с некоторых пор придерживается следующего правила: поколения с нечетным номером (UltraSPARC I, III и т.д.) представляют собой разработки, имеющие принципиально новую архитектуру (новый конвейер), а с четным номером (UltraSPARC II, IV и т.д.) – являются технологической модернизацией предыдущего поколения. При таком подходе обеспечивается программная совместимость при переходе от одного поколения к другому и обеспечивается постоянный рост производительности микропроцессоров. Опыт последних нескольких лет свидетельствует в пользу такого подхода.

Завершая эту тему, нельзя не сказать несколько слов о дальнейших планах Sun по разработке новых микропроцессоров. Речь будет идти, в основном, о семействе «S», как базовом для всего направления, но сначала – о серьезных переменах в семействе «E». Совсем недавно, в мае 1999 года, компания представила архитектуру нового представителя семейства встроенных процессоров – UltraSPARC IIe, который должен появиться в 2000 году и сменить поколение процессоров microSPARC. Примечательно то, что с этого момента все процессоры, выпускаемые компанией, будут полностью совместимы на программном уровне (напомним, что выпускаемый сейчас microSPARC представляет собой 32-разрядный процессор с архитектурой V8, которая использовалась до появления линии UltraSPARC) (см. также [4]).

В 1998 году, когда стало ясно, что появление нового процессора UltraSPARC III задерживается, компанией были предприняты серьезные шаги по предотвращению возможных негативных последствий (см. [5]). Для этого была проведена модернизация процессоров второго поколения с целью повышения тактовой частоты.

Сначала появились процессоры с рабочей частотой 360 МГц (до этого было только 300 МГц), а затем – с частотами 400 и 450 МГц. Таким образом, был обеспечен постоянный рост производительности систем на базе процессоров UltraSPARC II.

В мае 1999 года появился первый опытный экземпляр процессора UltraSPARC III. Он выполнен по технологии 0.25 мкм и имеет рабочую частоту 600 МГц. Серийные образцы процессоров должны появиться уже к концу этого года. В дальнейшем за счет повышения технологических норм до уровня 0.18 мкм планируется поднять его производительность путем наращивания тактовой частоты до 1 ГГц.

В конце 2000 года Sun планирует приступить к выпуску нового процессора UltraSPARC IV, который будет изготовлен по технологии 0.15 мкм и должен иметь начальную рабочую частоту 1 ГГц. Это будет первый процессор UltraSPARC, выполненный по новой технологии с использованием меди в качестве проводников. (В настоящее время данная технология применяется ограниченным числом компаний, имеющих собственное производство. К их числу относится IBM, которая использует этот процесс при изготовлении своих новых процессоров семейства Power.)

В 2002 году ожидается появление представителя пятого поколения процессоров – UltraSPARC V, начальная рабочая частота которого должна составить 1.5 ГГц (см. [6]). При его изготовлении планируется использование технологии 0.07 мкм. Сейчас такие технологические нормы достижимы только в лабораторных условиях, однако, предполагается, что через три года это станет реальностью.

Более долгосрочных прогнозов не существует, да их пока и не может быть, поскольку никто сейчас не возьмется предполагать, какие проблемы ожидают разработчиков в более отдаленной перспективе.

3. Несколько слов о конкурентах

На сегодняшний день имеется ограниченное число компаний, разрабатывающих собственные высокопроизводительные процессоры класса UltraSPARC III. Это Intel (Merced), Compaq (Alpha), IBM (Power-3), Hewlett-Packard (PA-RISC) и SGI/MIPS (R1x000). Однако, не все они могут рассматриваться в качестве реальных конкурентов. Ситуация в этой области, на наш взгляд, такова.

Самым мощным потенциальным конкурентом UltraSPARC остается процессор Merced компании Intel. Однако, подробности его аппаратурной реализации скрыты от сторонних наблюдателей, к тому же появление первых образцов отложено до середины 2000 года. Как увидим дальше, это оказало очень большое влияние на стратегию некоторых компаний.

Hewlett-Packard участвует в проекте создания Merced, и до последнего времени было не очень ясно, насколько серьезны ее планы по продолжению развития линии собственных микропроцессоров PA-RISC. Однако, в ноябре 1998 года компанией был представлен новый процессор PA8500, выполненный по технологии 0.25 мкм. При этом было подтверждено намерение и дальше продолжать разработку процессоров этого семейства параллельно с участием в проекте Merced. Создается впечатление, что данное решение появилось вследствие задержки выпуска Merced, с которым связывались большие надежды. Правда, оно (решение) может оказаться несколько запоздалым, свидетельством чему является переход компании Texas Instuments с рабочих станций HewlettPackard на оборудование Sun [8], хотя все это может быть обусловлено и другими причинами.

Очень похожая ситуация сложилась с процессорами MIPS. Еще год назад представители SGI утверждали, что собираются переводить свои рабочие станции на Merced, и R12000 – последний используемый ими процессор. Однако, в марте этого года в Токио были обнародованы новые планы компании [7]. Согласно им, SGI собирается поддерживать оба направления, как и Hewlett-Packard. Новый процессор от MIPS – R14000 – появится в середине 2000 года, примерно в одно время с Merced. Что касается его производительности, то, как и у PA-8500, она уступает UltraSPARC III.

Процессор Power-3 корпорации IBM сможет конкурировать с UltraSPARC III, только когда достигнет тактовой частоты 500 МГц (сейчас – лишь 200 МГц).

Таким образом, остается только один реальный конкурент – Alpha 21264. Это процессор, который уже достаточное время выпускается и сейчас идет работа по повышению его тактовой частоты. Alpha 21264 имеет производительность, которая по некоторым показателям превышает уровень UltraSPARC III. В силу перечисленных причин, именно этот микропроцессор чаще всего используется для сравнения с процессором компании Sun Microsystems.

4. Архитектура процессора UltraSPARC III и ее особенности

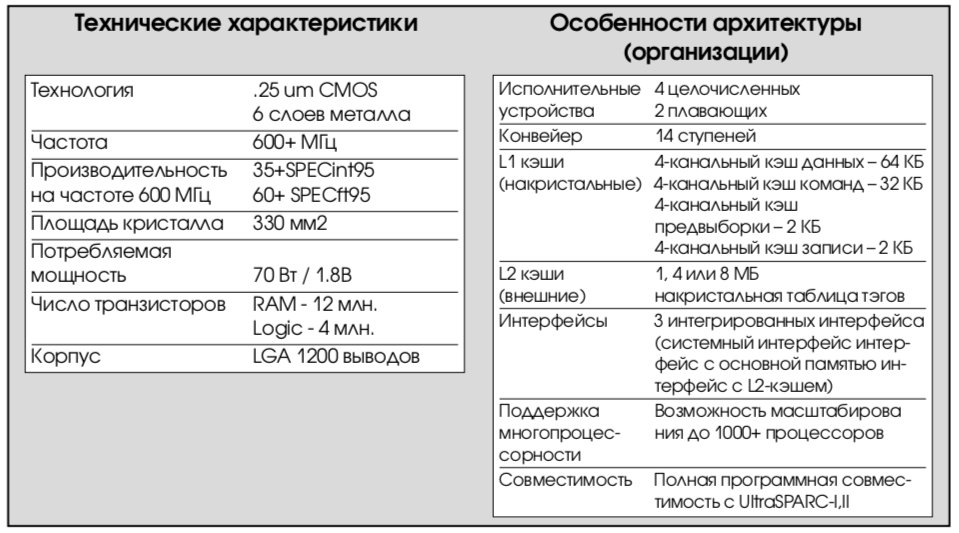

Новый процессор создавался для того, чтобы заменить микропроцессоры второго поколения семейства UltraSPARC. Он имеет производительность, в 2-3 раза превышающую показатели 300-мегагерцовых процессоров UltraSPARC II. Помимо этого, архитектура процессора разрабатывалась с учетом использования его в масштабируемых многопроцессорных системах. В табл. 1 приведены основные характеристики нового изделия. Ниже будут рассмотрены отдельные архитектурные решения, помогающие процессору «набирать очки» в борьбе за повышение производительности.

4.1. Краткое описание архитектуры

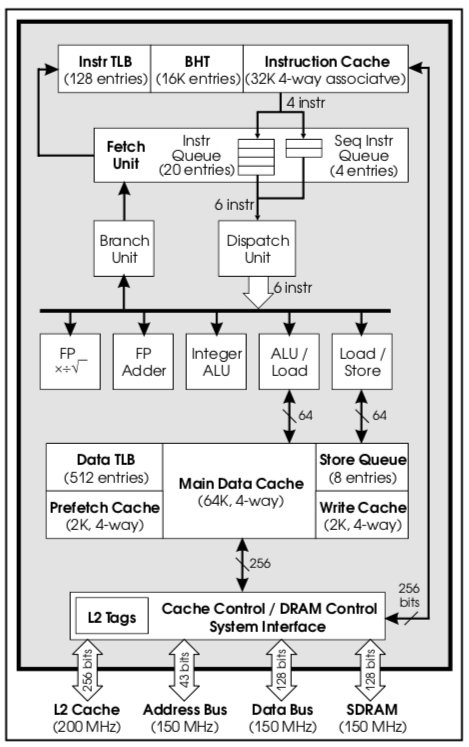

UltraSPARC III представляет собой высокопроизводительный суперскалярный микропроцессор, предназначенный для использования в мощных рабочих станциях и серверах. Он ориентирован на работу в масштабируемых микропроцессорных комплексах. На рис. 2 приведена структурная схема процессора. В его состав входят следующие основные функциональные блоки:

- шесть исполнительных устройств (4 целочисленных и 2 плавающих);

- кэш-памяти команд и данных объемом 32 КБ и 64 КБ соответственно;

- кэши предвыборки и записи объемом по 2 КБ каждый;

- системный интерфейс;

- контроллер основной памяти;

- контроллер кэша второго уровня (L2 кэш);

- таблица тэгов L2 кэш.

Функции исполнительных устройств распределяются следующим образом.

Целочисленные: 2 АЛУ (Integer ALU, ALU/Load), специализированное исполнительное устройство (Load/Store) и устройство обработки ветвлений (Brach Unit).

Плавающие: устройства плавающей арифметики/графики (FP adder, FP mul/div/sqrt).

Далее будут рассмотрены особенности архитектуры. При этом выбираются те моменты и решения, которые, на наш взгляд, являются определяющими для данного процессора.

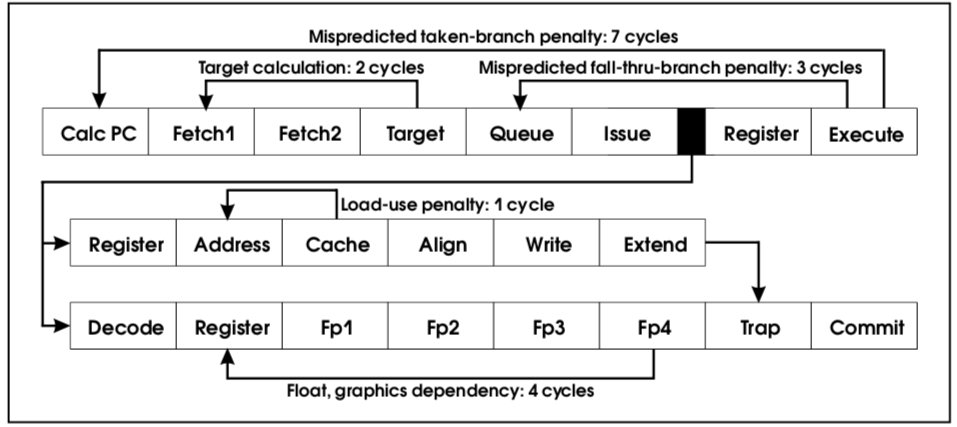

4.2. Конвейер

Основу архитектуры любого процессора составляет конвейер. Без понимания его работы трудно разобраться в необходимости и порядке взаимодействия перечисленных выше устройств.

UltraSPARC III имеет 14-ступенчатый конвейер (см. рис. 3). На сегодняшний день это, пожалуй, самый длинный конвейер среди серийных процессоров. Почти половина его (6 ступеней) отводится на подготовку к выполнению команд, столько же – на исполнение команд; две последние ступени – завершающие.

Исполнительная часть конвейера состоит из двух частей: целочисленной и плавающей. Обе части имеют одинаковую длину, что упрощает согласование их работы (позволяет выдавать результаты вычислений в порядке их запуска на исполнение). Аналогичное решение (выровненные конвейеры целочисленной и плавающей арифметики) успешно использовалось в предшествующих поколениях микропроцессоров UltraSPARC.

Большое количество ступеней конвейера, по-видимому, объясняется существенным повышением тактовой частоты процессора. Более короткие фазы выполнения позволяют избежать длинных связей на кристалле, которые при столь малых технологических нормах начинают вносить заметную дополнительную задержку. Те операции, которые не вписываются в один такт, как, например, выборка команд из кэша, разбиваются на более мелкие процедуры и выполняются за 2 такта.

Следует отметить еще одну особенность, связанную с исполнительной частью целочисленного конвейера. Для выполнения целочисленных команд отводится 4 такта, реально на это уходит меньше времени (команды АЛУ выполняются за 1 такт). Однако, выровненный конвейер позволяет получить на выходе результаты в том порядке, в котором они поступили на исполнение.

4.3. Порядок запуска команд на исполнение

В отличие от многих других современных процессоров, использующих механизм произвольного запуска команд на исполнение, то есть не в порядке их расположения в программе, UltraSPARC III действует строго по порядку. По утверждениям разработчиков, это позволяет сократить объем логики управления в ядре процессора (которая при разработке ее топологии требует большого объема ручной работы), что благоприятно сказывается на быстродействии.

Таким образом, в новом процессоре, как и в его предшественниках, запуск команд на исполнение происходит в порядке их расположения в программе. Процессор позволяет одновременно запустить на исполнение до шести команд (по числу исполнительных устройств); правда, средневзвешенное число одновременно запускаемых команд равно четырем.

После выборки команды попадают в буфер (очередь) команд на 20 элементов (Instruction Queue), откуда группами направляются в соответствующие исполнительные устройства. Максимальное число команд в группе – 6. Все команды в группе получают идентификационный код, в соответствии с которым на выходе из конвейера будут сложены их результаты.

Выше уже упоминалось, что время выполнения большинства целочисленных команд существенно меньше длины исполнительной части целочисленного конвейера, и что фиксированная длина конвейера обеспечивает сохранение порядка поступления команд. Однако, это не означает, что результаты становятся доступны только по достижению выхода конвейера. На самом деле полученные данные могут быть использованы другими командами, находящимися на стадии выполнения, уже на следующем такте после получения результата. Это возможно благодаря наличию рабочего регистрового файла, в котором хранятся все промежуточные результаты вычислений и из которого, по завершению исполнения группы команд, эти результаты переписываются в архитектурный регистровый файл. Таким образом, реальная эффективность конвейера заметно повышается.

4.4. Механизм предсказания ветвлений

Устройство предсказания ветвлений является непременным атрибутом любого современного высокопроизводительного микропроцессора, однако, в каждом конкретном случае оно реализовано по-своему. Основная задача данного устройства состоит в сокращении накладных расходов из-за нарушений в работе конвейера при ветвлении программ. Если взглянуть на конвейер UltraSPARC III (рис. 3), то хорошо видно, сколько придется заплатить за неправильно предсказанный переход. Штрафные санкции составят 7 дополнительных тактов (кстати, у Alpha 21264 – столько же при меньшей длине конвейера). Есть за что бороться.

При решении данной задачи разработчики процессора решили использовать достаточно простой одноуровневый механизм (в отличие от двухуровневого адаптивного механизма в Alpha 21264). Он представляет собой таблицу на 16 К значений, содержащую информацию об уже происшедших ветвлениях и обеспечивает точность предсказаний на уровне 95% на тестах SPEC95.

Помимо механизма предсказания ветвлений в процессоре используется еще и стек адресов возврата на 8 значений, а также очередь последовательных команд (Sequential Instruction Queue), которая хранит до четырех команд, следующих за командой ветвления, но соответствующих альтернативному пути. В случае, когда предсказанное ветвление окажется неверным, команды из этой очереди сразу направляются на исполнение, экономя несколько тактов.

4.5. Особенности реализации внешних интерфейсов микропроцессора

Производительность вычислительной системы зависит от многих факторов, среди которых быстродействие процессора – не самый главный. Очень многое определяет то, как он взаимодействует с другими компонентами системы.

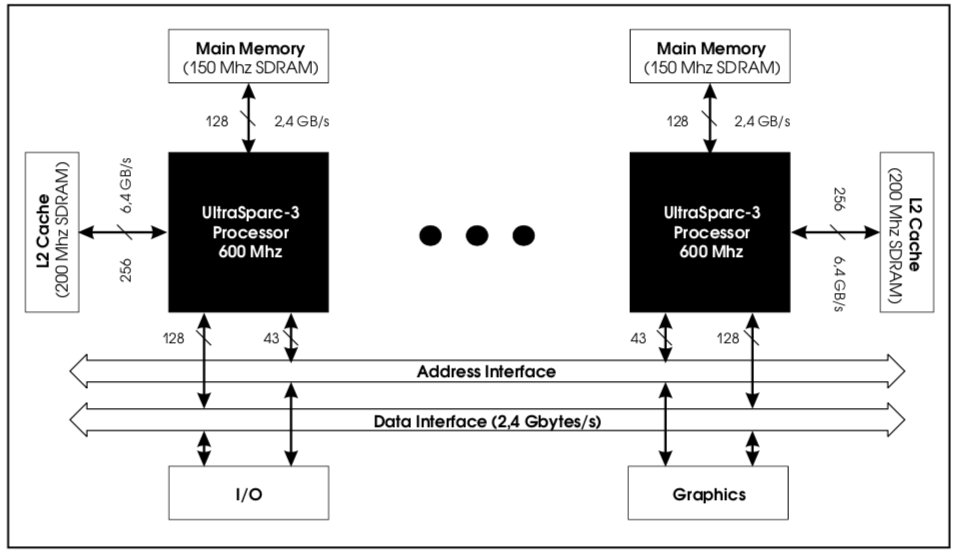

На рис. 4 приведен пример многопроцессорной системы, реализованной на основе UltraSPARC III. Рассмотрим и проанализируем некоторые ее детали. Первое, что сразу обращает на себя внимание, это большое количество внешних интерфейсов у процессора. Их три: 128-разрядный канал обмена с основной памятью (Main Memory), 256-разрядный канал обмена с кэш-памятью второго уровня (L2 Cache) и 128-разрядный системный интерфейс.

Достаточно очевидно, что такая многошинная архитектура способствует более эффективной работе многопроцессорной системы в целом. Правда, это новое качество недешево обходится (это и дополнительные расходы на разработку нового корпуса с рекордным числом выводов – 1200, и проблемы повышенного энергопотребления как самого процессора, так и микросхем чипсета и т.п.). Но, похоже, конечный результат стоит того. Рассмотрим подробнее каждый из перечисленных интерфейсов.

4.5.1. Интерфейс с основной памятью

Поскольку архитектура процессора подразумевает единоличное владение данной памятью, то есть отсутствие непосредственного доступа к ней со стороны каких-либо других устройств, появляется возможность достижения максимальной пропускной способности данного канала, для чего предусмотрен накристальный контроллер памяти. Такое решение имеет следующие положительные стороны.

Во-первых, отпадает необходимость в дополнительных внешних компонентах, то есть упрощается сопряжение процессора и памяти. Это к тому же приводит еще и к снижению стоимости.

Во-вторых, возрастает пропускная способность, поскольку производительность канала зависит только от параметров памяти. Так, при использовании SDRAM с тактовой частотой 150 МГц пропускная способность составит 2.4 ГБ/с.

4.5.2. Канал обмена с L2 кэш-памятью

По своей реализации данный канал напоминает описанный выше. Однако, здесь есть ряд принципиальных особенностей.

Во-первых, канал имеет более высокую разрядность – 256 бит. На сегодняшний день UltraSPARC III, пожалуй, единственный микропроцессор, имеющий такую широкую шину данных кэша второго уровня. При использовании микросхем статической памяти (SRAM), работающих на частоте 200 МГц, пропускная способность данного канала способна достичь 6.4 ГБ/с. И это не предел.

Во-вторых, по аналогии с накристальным SDRAM-контроллером канала основной памяти, данный интерфейс имеет накристальную таблицу тэгов вторичного кэша. Размер таблицы составляет 90 КБ, и этого достаточно для поддержания кэш-памяти объемом до 8 МБ.

Основным достоинством такого решения является то, что работа с таблицей осуществляется на частоте процессора, то есть результат обращения к кэшу становится известен гораздо раньше, чем в случае внекристального расположения таблицы тэгов. Соответственно, при непопадании в кэш процедура инициализации обращения к основной памяти начинается на несколько тактов раньше. Аналогично обстоит дело и с поддержкой когерентности кэшей в многопроцессорных системах.

Перечисленные преимущества отчасти можно отнести и к контроллеру SDRAM, однако, там производительность канала в меньшей степени зависит от быстроты работы контроллера.

4.5.3. Особенности реализации канала записи в L2 кэш-память

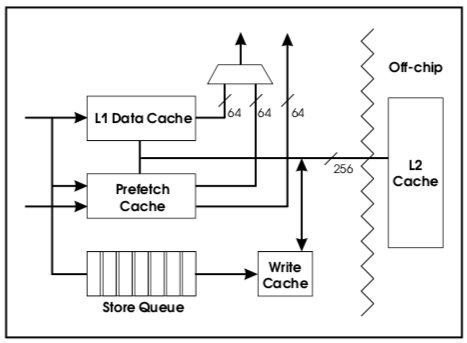

Процедура записи, использованная в UltraSPARC III, может показаться слишком сложной с точки зрения аппаратурной реализации (см. рис. 5), однако, на самом деле это не так.

Канал записи состоит из трех основных частей: очереди на 8 слов (Store Queue), кэш-памяти данных первого уровня (L1 Data Cache) и кэш-памяти записи (Write Cache). Сразу же отметим, что кэши имеют различные механизмы обновления: L1 кэш данных – сквозной записи, а кэш записи – отложенный. Далее будет понятно, зачем это нужно.

Сначала сохраняемая информация записывается в очередь. Это происходит во время выполнения команды сохранения. Затем, после завершения команды, данные записываются в L1 кэш и, одновременно, в кэш записи. При этом, если происходит непопадание в L1 кэш, то его содержимое не обновляется. В противном случае из-за сквозного режима обновления данной кэш-памяти происходило бы постоянное обращение ко вторичному кэшу. Таким образом, кэш-память записи как бы дополняет и дублирует L1 кэш, но только в процессе записи. По утверждениям разработчиков, использование такой организации канала записи позволяет сократить трафик на шине вторичной кэш-памяти на 90%.

4.5.4. Системный интерфейс

Системный интерфейс по своим характеристикам аналогичен каналу основной памяти. Из специфических механизмов, свойственных только ему, следует отметить поддержку многопроцессорности (до четырех процессоров в конфигурации с общей шиной и более четырех при иерархической структуре шин).

Подводя итог всему сказанному об организации внешних интерфейсов процессора UltraSPARC III, можно отметить следующее.

Во-первых, многошинная структура позволяет легко строить на базе данного процессора как однопроцессорные, так и многопроцессорные системы. При этом число процессоров в системе практически не ограничено (1000 и больше).

Во-вторых, использование накристальной логики управления каналами позволяет масштабировать их пропускную способность, увеличивая производительность с ростом рабочей частоты процессора и появлением более быстрой памяти.

В-третьих, структура внешних связей процессора позволяет легко сделать на его основе модификацию для недорогих серверов.

5. Заключение

Мы рассмотрели некоторые аспекты маркетинговой политики компании Sun Microsystems, ее ближайшие и перспективные планы в области разработки микропроцессоров, а также особенности архитектуры нового микропроцессора UltraSPARC III, с которым многие из этих планов тесно связаны.

При описании архитектуры процессора упор был сделан на особенности его организации, которые позволяют данному изделию успешно конкурировать с продукцией других компаний.

В заключение хотелось бы отметить, что, несмотря на задержку в появлении, процессор имеет очень хорошие шансы на успех. Причин тому две. Во-первых, характеристики UltraSPARC III очень хороши как по нынешним меркам, так и по меркам ближайшего будущего. Во-вторых, многие конкуренты слишком поздно среагировали на изменение ситуации в области высокопроизводительных микропроцессоров.

6. Литература

1. UltraSparc-3 Aims at MP Servers. – Microprocessor Report, Vol. 11, N 14, Oct 27, 1997.

2. UltraSPARC on the Road to 1.5 GHz in 2002. – Sun Microsystems, 1998. http://www.sun.com/microelectronics/roadmap/.

3. Sun Unveils Third Generation UltraSPARC-III Microprocessor Family. – Sun Microsystems, 1997. http://www.sun.com/smi/Press/sunflash/9710/sunflash.971006.1.html.

4. Sun Targets Embedded Communications Market With 64-bit UltraSPARC IIe. – Sun Microsystems, 1999. http://www.sun.com/smi/Press/sunflash/9905/sunflash.990504.3.html.

5. Sun Unveils Comprehensive SPARC Roadmap. – Sun Microsystems, 1998. http://www.sun.com/ smi/Press/sunflash/9809/sunflash.980901.1.html.

6. Sun aims at Intel's Merced. – CMPnet, Issue 1125, Sept. 07, 1998. http://www.techweb.com/.

7. Silicon Graphics Detail MIPS Road Map. – http://www.techweb.com/.

8. HP Moves Slowly On Merced Migration. – http://www.techweb.com/.

9. http://www.sun.com/microelecronics/.

Решения компании Sun Microsystems для шины CompactPCI

1. Роль стандартов

Слово «стандарт» является ключевым для современных информационных технологий. Обычно, рассматривая роль стандартов, обращают внимание, прежде всего, на взаимную совместимость (интероперабельность) решений разных производителей. Однако, не менее важным вопросом является сокращение сроков разработки информационных систем и их компонентов, возможное благодаря унификации способов и средств разработки, стандартизации интерфейсов, наличию готовых, настраиваемых решений, способных удовлетворить потребности различных категорий заказчиков.

Важно подчеркнуть, что сокращение сроков разработки новых продуктов, разумеется, должно происходить без снижения качества. К сожалению, на практике так получается не всегда. Желание обогнать конкурентов, расширить «свою» долю рынка толкает на выпуск сырых, плохо отлаженных систем. Если же система строится на основе стандартов и стандартных компонентов, объем новых аппаратуры и программ, количество новых связей минимизируется, что позволяет выполнять в сжатые сроки не только собственно разработку, но и качественное тестирование.

Еще одна важная функция стандартов состоит в защите систем от морального старения. Продуманные, отработанные спецификации изначально строятся в расчете на перспективу, на наращивание количественных и качественных характеристик; эти свойства передаются и продуктам, созданным на основе подобных стандартов.

Стандарты аккумулируют в себе требования определенных предметных областей. Такие области, как промышленные применения и телекоммуникации, предъявляют дополнительные требования к аппаратуре в части ее конструктивного исполнения (модульность, стойкость к промышленным воздействиям – вибрации, ударам и т.п., хороший теплоотвод).

На наш взгляд, все перечисленные достоинства присущи стандарту CompactPCI, разработанному группой PICMG (PCI Industrial Computer Manufacturers Group), в которую входят более 450 компаний – производителей промышленных и телекоммуникационных систем.

2. CompactPCI как стандарт для промышленных и телекоммуникационных систем

Стандарт CompactPCI распространяется на электрический, логический и программный уровни. Его можно рассматривать как объединение

двух стандартов: PCI, известного по настольным системам, а также хорошо зарекомендовавшего себя в области промышленных применений стандарта «Евромеханика».

CompactPCI предусматривает архитектуру с пассивной соединительной панелью, в которую устанавливается до восьми плат (против четырех для обычного PCI). Эти платы выполнены в стандарте евромеханики с размерами 100 на 160 мм (так называемый формат 3U) или 233.35 на 160 мм (формат 6U). Платы CompactPCI монтируются в стандартные стойки для телекоммуникационного оборудования в вертикальном положении, что способствует лучшей естественной и принудительной вентиляции.

Стандарт CompactPCI определяет ряд мер, направленных на мягкую установку и надежное закрепление плат, устойчивость к ударам и вибрации, что важно для промышленных систем. Кроме того, обеспечивается удобство обслуживания и, как следствие, минимизируется время ремонтных процедур.

Программная совместимость с PCI дает возможность вести разработки программного обеспечения для CompactPCI на обычных настольных системах, в привычном окружении. Впрочем, в настоящее время существует широкий выбор удобных средств кросс-разработки, где в качестве инструментальной используется, как правило, платформа SPARC/Solaris.

Стандарт CompactPCI, несомненно, является жизнеспособным, развиваемым. Он гарантирует высокую пропускную способность по вводу/выводу (132 МБ/сек при частоте 33 МГц и разрядности 32; стандарт предусматривает рост этого значения за счет увеличения разрядности до 64) и плотность расположения компонентов, наращивание числа устанавливаемых плат за счет применения микросхем-мостов. Один из подкомитетов PICMG специфицировал поддержку горячей замены плат (существенное требование для промышленных и телекоммуникационных систем).

Широкая поддержка стандарта CompactPCI ведет к наличию большого числа готовых решений, что помогает минимизировать время изготовления новых систем. Большие объемы производства способствуют снижению цен на модули для CompactPCI.

Рынок систем CompactPCI быстро и устойчиво развивается. Ожидается, что в 2001 году он перешагнет рубеж в 1 миллиард долларов.

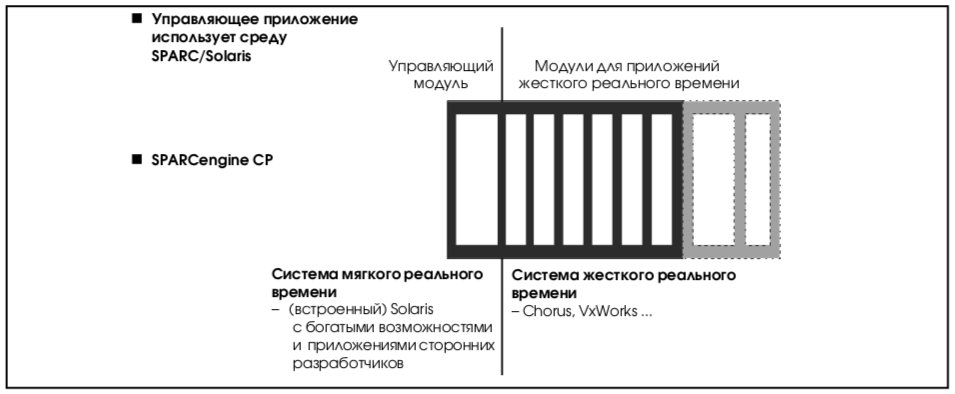

3. Аппаратная и программная архитектура встроенных систем с шиной CompactPCI

Обычно системы в стандарте CompactPCI представляют собой набор одноплатных модулей. Часть модулей функционирует в режиме жесткого реального времени, обеспечивая управление, поддерживая коммуникации и т.п.; другие модули могут выполнять координирующие действия, реализовывать (графический) диалог с оператором, то есть функционировать в режиме мягкого реального времени (см. рис. 1). При наличии повышенных требований к готовности часть модулей может дублироваться.

В качестве программной платформы модулей CompactPCI-систем используются ОС реального времени (такие как VxWorks компании Wind River Systems или ChorusOS Sun Microsystems) или универсальные ОС, такие как Solaris.

Выбор архитектуры систем, включающих в себя модули с существенно разными функциями и, соответственно, требованиями, является сложным, прежде всего, с психологической точки зрения. Обычно разработчикам хочется оставаться в рамках одной программной платформы, которая в таком случае оказывается операционной системой реального времени (ОС РВ). На ОС РВ возлагаются такие несвойственные ей функции, как поддержка графического диалога с оператором, взаимодействие с базами данных и т.п.

На наш взгляд, для подобных конфигураций предпочтительнее воспользоваться архитектурой клиент/сервер, устанавливая на каждый модуль ту ОС, которая наиболее естественным образом выполняет необходимые функции. SPARC/Solaris – идеальная платформа для координирующих модулей, обладающая высокой производительностью и достаточной реактивностью, не говоря уже о богатстве возможностей.

Для модулей жесткого реального времени могут использоваться аппаратные продукты, которые мы рассмотрим в следующем разделе.

4. Аппаратные продукты Sun для шины CompactPCI

Компания Sun Microsystems способна предложить полное решение при создании широкого спектра CompactPCI-систем – от аппаратных модулей до операционных систем и прикладных компонентов. Мы ограничимся рассмотрением аппаратных аспектов, поскольку именно они специфичны для CompactPCI.

Семейство модулей SPARCengine CP, предназначенных для использования в системах CompactPCI, состоит в настоящее время из трех продуктов:

- плата SPARCengine CP1500 с процессором UltraSPARC IIi;

- плата SPARCengine CP1400 также с процессором UltraSPARC IIi;

- плата SPARCengine CP1200 с процессором microSPARC IIep.

Краткие сведения о микропроцессорах UltraSPARC IIi и microSPARC IIep можно найти в разделе «Стратегия компании на ближайшие несколько лет» статьи А. Шадского «Архитектура процессора UltraSPARC III», помещенной в этом же номере Jet Info.

В качестве операционной системы для SPARCengine CP может использоваться Solaris, что позволяет получить полностью 64-разрядное решение с большим числом готовых приложений. На SPARCengine CP портированы ОС реального времени ChorusOS и VxWorks, занимающие ведущие позиции в своем классе.

Далее мы детально рассмотрим платы SPARCengine CP1500 и SPARCengine CP1400, но перед этим позволим себе несколько замечаний о роли процессоров UltraSPARC в телекоммуникационных системах.

Современным телекоммуникационным системам, в развитии которых очевидна тенденция к быстрому расширению спектра предоставляемых услуг, необходимо сочетание универсальных и специализированных процессоров, прежде всего, цифровых процессоров сигналов (DSP).

Исторически, однако, сложилось так, что мир DSP оказался обособленным, со своими операционными системами (а часто и без каких-либо ОС), со специфическими средствами разработки (зачастую – с программированием в кодах) и т.п. Желание выжать максимум производительности для DSP впрямую противоречит скорости разработки.

Дополнительный набор команд поддержки мультимедиа (VIS), реализованный в микропроцессорах UltraSPARC, покрывает большинство функций, традиционно возлагаемых на цифровые процессоры сигналов. Это дает надежду на сближение операционных сред и средств разработки для универсальных и DSP-процессоров, что сулит огромный выигрыш и по времени разработки, и по затрачиваемым ресурсам.

4.1. SPARCengine CP1500

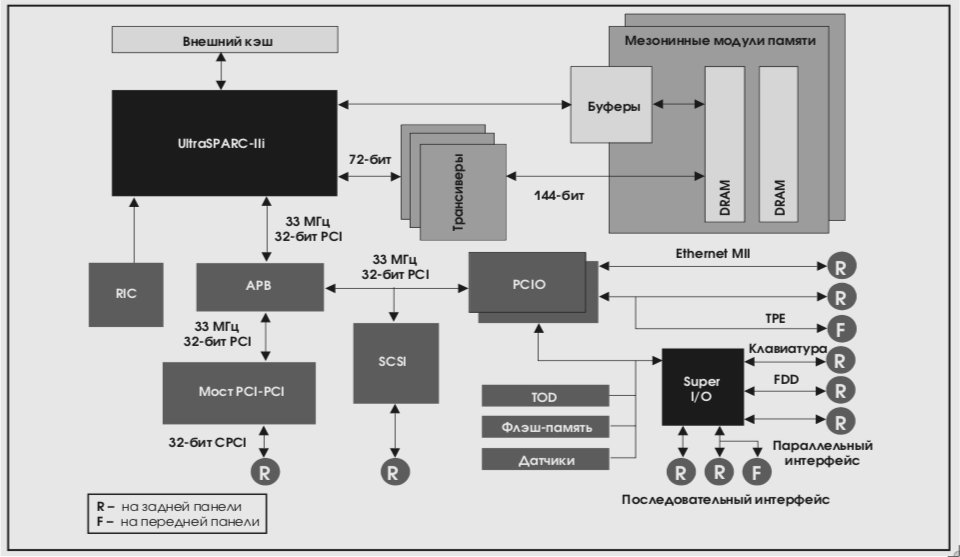

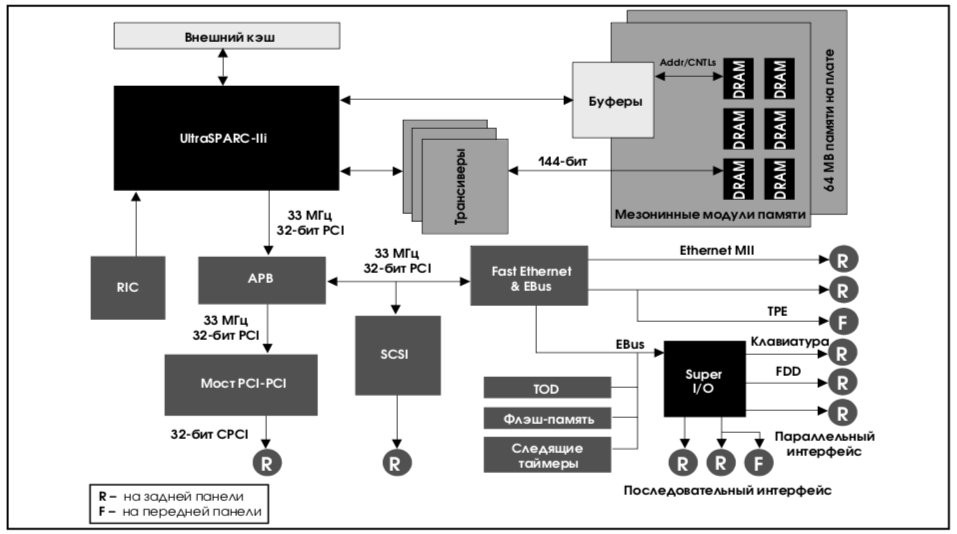

Плата SPARCengine CP1500 принадлежит к числу высокопроизводительных продуктов для CompactPCI, являясь 64-разрядной и с аппаратной, и с программной точек зрения. Ее аппаратная схема приведена на рис. 2.

Ключевым элементом SPARCengine CP1500 является процессор UltraSPARC IIi. На момент написания статьи максимальная доступная тактовая частота составляла 333 МГц; согласно материалам компании, в ближайшее время ожидается ее увеличение до 425 МГц.

На плате может быть установлено до двух мезонинных модулей ECC-памяти. Емкость одного модуля – от 64 до 512 МБ. Соответственно, общий объем оперативной памяти может достигать 1 ГБ. Кроме того, доступна флэш-память (до 8МБ) и память для начального загрузчика (1 МБ).

На SPARCengine CP1500 располагаются две внутренние шины PCI с тактовой частотой 33 МГц, гарантирующие высокую эффективность подсистемы ввода/вывода, в состав которой входят интерфейс Ultra-Wide SCSI-2 с пропускной способностью 40 МБ/с, двухканальный 10/100 Ethernet и другие традиционные компоненты. Одна из внутренних шин используется для подключения внешних интерфейсов, а вторая выходит через мост на шину CompactPCI.

Среди достоинств SPARCengine CP1500 выделим следующие:

- сочетание однослотовой конструкции с вычислительной мощью и большим объемом памяти, наличие дополнительных команд поддержки мультимедиа (VIS);

- высокая пропускная способность по вводу/выводу;

- типоразмеры, стандартные для промышленных и телекоммуникационных систем;

- двоичнаясовместимостьскомпьютерамиSun. SPARCengine CP1500 может применяться в гражданских и военных системах, в том числе в системах жесткого реального времени.

4.2. SPARCengine CP1400

SPARCengine CP1400 (см. рис. 3) можно рассматривать как вариант SPARCengine CP1500, оптимизированный по параметру производительность/стоимость. Тактовая частота процессора UltraSPARC IIi в данном случае составляет 300 МГц. На плате размещается 64 МБ оперативной памяти. Этот объем может быть увеличен до 832 МБ за счет мезонинных модулей.

В SPARCengine CP1400 оставлен один канал 10/100 Ethernet, несколько уменьшена по сравнению с SPARCengine CP1500 суммарная пропускная способность подсистемы ввода/вывода. В результате удалось на треть и более снизить стоимость платы, оставшись на достаточно высоком уровне производительности.

Очень полезен для программирования систем жесткого реального времени следящий таймер (Watchdog Timer), присутствующий в SPARCengine CP1400. Он помогает контролировать длительность критически важных операций и, в случае превышения лимита, выполнять необходимые действия вплоть до перезагрузки системы.

Следует еще раз подчеркнуть, что для одноплатных компьютеров семейства SPARCengine CP имеются мощные средства разработки (в том числе кросс-средства), предлагаемые как самой Sun Microsystems, так и другими компаниями (например, Wind River Systems). Заказчики вольны выбирать операционную платформу и для любой из них они смогут быстро и с удобствами разрабатывать приложения. Это еще раз доказала состоявшаяся в Хельсинки 21-24 июня 1999 года выставка VON Europe'99 (VON – передача голоса по сети).

Представленные на выставке разработки компаний Telesoft Design, Westek, Intraserver Technology и Znyx Corp. подтвердили прочные позиции Sun в области услуг телефонии, обладающих важнейшим качеством высокой готовности. Была продемонстрирована первая в мире CompactPCI-платформа для разработки SMS-решений (служба коротких сообщений) для мобильной связи.

5. Заключение

Когда речь идет о разработках компании Sun Microsystems, неизменно отмечаются такие характеристики, как комплексность, высокое качество и следование стандартам. Этими характеристиками в полной мере наделены продукты Sun для CompactPCI. На наш взгляд, данное направление заслуживает самого пристального внимания со стороны отечественных заказчиков и производителей комплектного оборудования. Продукты Sun позволяют создавать решения различного класса для разных прикладных областей, но всегда в основе этих решений будет лежать экономическая целесообразность, интероперабельность, возможность развития.

Подписаться

Подписаться Читать в телеграм

Читать в телеграм